|

||||||||

|

|

|

|

|||||||

| DRAM 依設計架構及處理速度分類,可分為 FPM ( Fast Page Mode ) DRAM 、 EDO ( Extended Data Out ) DRAM 及 SDRAM ( Synchronous DRAM )三類,其中 FPM DRAM 開發最早,速度最慢, EDO DRAM 次之, SDRAM 最快並為目前市場的主流。在 SDRAM 之後所推出更快速的 DRAM 架構則以 DRDRAM ( Direct Rambus DRAM )及 DDR ( Double Data Rate ) SDRAM 為主,其中 DRDRAM 與目前主流 SDRAM 技術差異大,良率不高,面積亦較大、封裝測試成本較高使設備及生產成本較難降低,並有權利金的問題,市場接受度不高,目前多在工作站、 P4 初期市場等高階市場發展,以英特爾為主導廠商。而 DDR/DDR2 與 SDRAM 技術相近,並可沿用 SDRAM 的生產設備,生產成本僅較 SDRAM 增加 1 成,無權利金的問題,成為主流。 過去 PC 市場持續重複「 CPU 性能提升 → OS 與應用程式功能增強 → 硬體(記憶體)需求提高」的週期循環,如今此一週期的時間將拉長。電腦不是推動記憶體消耗的唯一市場,消費電子產品、網路和通訊市場也已開始成長。 |

|||||||

研發團隊成立之初 ,即專注在記憶體領域,本公司自行研發設計,PC-based DRAM 記憶體測試平台的軟硬體設備 ,同時提供客戶完整SDRAM、DDR、DDR2客制化 Die 與 IC 測試服務,累積 測試核心技術包括:

當記憶體進入 90nm 、 65nm 奈米製程之後,設計 技術逐步走向 High Bit Density 、 High Speed 、 Low Power 。原來的 PC 測試平台受限於 BIOS 與 Chipset 架構,是無法精準測試記憶體重要參數 (Key Parameter) 需求;新規劃的測試平台是可以經準調整工作頻率、電壓與電流,同時可以測試 DDR 、 DDR2 、 SRAM 、 FLASH 各類 記憶體,同時提供 TSOP 、 BGA 測試介面 。 |

|||||||

DRAM 是半導體技術發展最成熟、應用範圍最廣泛、使用量最大的記憶體;從 Server Workstation 、 Desktop 、 Notebook 電腦主機到 Disk Controller 、網路卡、顯示卡、 DVD player 。 DRAM 產品朝向 High Bit Density, High Speed, Low Power 設計,製程技術也一直使用 0.13um 、 0.11um 、 90nm 、 65nm 先進製程。  當 記憶體 IC 元件經過測試機台,完整的PC測試驗證手續, 應用系統與 測試環境大多仍不盡相同 。真實的應用 系統有不同的使用範圍,例如:PC記憶體模組、DVD player、Router 。 系統整合測試是記憶 體元件 測試 很重要的一環 。 系統整合測試 的過程 ,首先必須修改應用系統 PCB 佈局設計,記憶體元件相關的電路,增加 DRAM 測試記憶體元件電路,容許放置各種型態記憶體元件,然後 系統開機直接測試記憶體 IC 元件正常與否 。 系統測試的目的是在確保記憶體IC,最後誤差範圍在1%之內 。對於部分良品 (Bin2) 的應用 ,系統需稍作微調,因而系統測試需求更是重要 。 |

|||||||

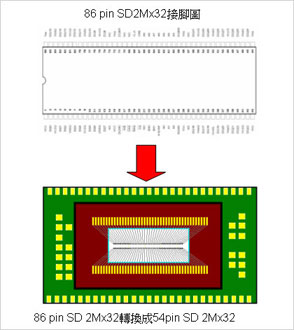

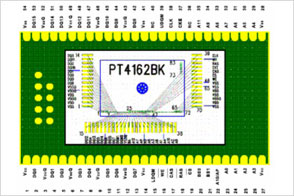

Smart Package 技術,是以公司現有的 DRAM 記憶體 Die 與 IC 測試驗證平台技術為基礎,提出從記憶體元件接腳、型態、降階容量轉換等方法,透過 DRAM 相關聯技術,整合測試軟體分類、 PCB 佈局與結合 COB(Chip-On-Board) 封裝方式,達到 DRAM 記憶體降低封裝成本與增加記憶體彈性應用的空間。 ( 例 1). 元件接腳轉換 ( 例 BGA->TSOP) 目前許多 DRAM 元件,為了高容量體積小,而產生堆疊的 BGA 封裝方式,其特性為接腳( Bonding pad ),朝四邊中的其中一邊,或以 L 型的排列。 Die 經過 Smart Package 封裝技術,可以改變封裝方式, DRAM 系統的應用範圍也因此更為廣泛 從硬碟控制系統,應用到 DVD 系統應用。 |

|||||||